サプライチェーンの奥深くでは、砂を完璧なダイヤモンド構造のシリコン結晶ディスクへと変える魔術師たちがいます。これは半導体サプライチェーン全体に不可欠な要素です。彼らは「シリコンサンド」の価値を1000倍近く高める半導体サプライチェーンの一部です。ビーチでかすかに見える光はシリコンです。シリコンは脆さと固体のような金属性(金属的性質と非金属的性質)を持つ複雑な結晶です。シリコンはどこにでも存在します。

シリコンは地球上で酸素に次いで2番目に多く、宇宙では7番目に多く存在する物質です。シリコンは半導体であり、導体(銅など)と絶縁体(ガラスなど)の中間の電気的特性を持ちます。シリコン構造に少量の異原子が混入すると、その挙動が根本的に変化する可能性があるため、半導体グレードのシリコンの純度は驚くほど高くなければなりません。電子部品グレードのシリコンの許容最低純度は99.999999%です。

これは、100億個の原子のうち、シリコン以外の原子はたった1個しか許容されないことを意味します。良質な飲料水には4000万個の水以外の分子が含まれており、これは半導体グレードのシリコンの5000万分の1の純度に相当します。

ブランクシリコンウェーハメーカーは、高純度シリコンを完全な単結晶構造に変換する必要があります。これは、適切な温度で溶融シリコンに単一の母結晶を投入することで行われます。母結晶の周囲に新しい娘結晶が成長し始めると、溶融シリコンからシリコンインゴットがゆっくりと形成されます。このプロセスは遅く、1週間かかることもあります。完成したシリコンインゴットの重量は約100キログラムで、3,000枚以上のウェーハを製造できます。

ウェーハは極細のダイヤモンドワイヤーを用いて薄片に切断されます。シリコン切断工具の精度は非常に高く、作業員は常に監視下に置かれなければなりません。さもないと、作業員は工具を使って髪の毛にひどいことをしてしまいます。シリコンウェーハの製造に関する簡潔な紹介は簡略化されすぎていて、天才たちの貢献を十分に評価できていませんが、シリコンウェーハ事業へのより深い理解を得るための背景情報として役立つことを願っています。

シリコンウェーハの需給関係

シリコンウェーハ市場は4社によって独占されており、長年にわたり、需要と供給の微妙なバランスが保たれてきました。

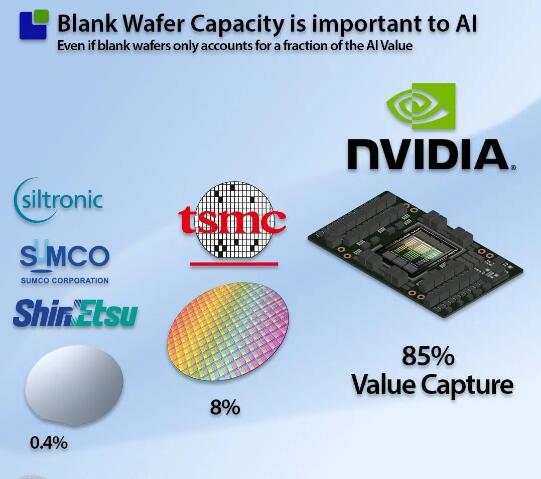

2023年の半導体売上高の減少により、市場は供給過剰状態に陥り、チップメーカーの社内在庫と社外在庫が高騰しています。しかし、これは一時的な状況に過ぎません。市場が回復するにつれて、業界はすぐに生産能力の限界に達し、AI革命によってもたらされる追加需要に対応しなければならなくなります。従来のCPUベースのアーキテクチャからアクセラレーテッドコンピューティングへの移行は、業界全体に影響を与えるでしょう。しかし、これは半導体業界の低価値セグメントにも影響を与える可能性があります。

グラフィックスプロセッシングユニット(GPU)アーキテクチャではより多くのシリコン領域が必要

パフォーマンスに対する需要が高まるにつれ、GPUメーカーはGPUからより高いパフォーマンスを得るために、いくつかの設計上の制約を克服しなければなりません。チップを大型化することは、もちろん、より高いパフォーマンスを実現する一つの方法です。電子は異なるチップ間を長距離移動することを好まないため、パフォーマンスが制限されるからです。しかし、チップを大型化することには、「網膜限界」と呼ばれる実用的な限界があります。

リソグラフィ限界とは、半導体製造に使用されるリソグラフィ装置において、1回の露光で露光できるチップの最大サイズを指します。この限界は、リソグラフィ装置、特にリソグラフィ工程で使用されるステッパーまたはスキャナの最大磁場サイズによって決まります。最新技術では、マスク限界は通常約858平方ミリメートルです。このサイズ限界は、1回の露光でウェーハ上にパターンを形成できる最大面積を決定するため、非常に重要です。ウェーハがこの限界よりも大きい場合、ウェーハを完全にパターン化するには複数回の露光が必要になり、複雑さとアライメントの課題から量産には現実的ではありません。新しいGB200は、粒子サイズ制限のある2つのチップ基板をシリコン中間層に組み合わせることで、2倍の大きさの超粒子制限基板を形成することで、この限界を克服します。その他の性能限界としては、メモリ容量とメモリまでの距離(つまりメモリ帯域幅)が挙げられます。新しいGPUアーキテクチャは、2つのGPUチップと同じシリコンインターポーザー上に搭載された積層型高帯域幅メモリ(HBM)を使用することで、この問題を克服しています。シリコンの観点から見ると、HBMの問題は、高帯域幅に必要な高並列インターフェースのため、各ビットのシリコン面積が従来のDRAMの2倍になることです。また、HBMは各スタックにロジック制御チップを統合するため、シリコン面積が増加します。大まかに計算すると、2.5D GPUアーキテクチャで使用されるシリコン面積は、従来の2.0Dアーキテクチャの2.5~3倍になります。前述のように、ファウンドリ企業がこの変化に対応できなければ、シリコンウェーハの生産能力は再び非常に逼迫する可能性があります。

シリコンウェーハ市場の将来の生産能力

半導体製造の3つの法則の1つ目は、最も少ない資金しか利用できないときに、最も多くの資金を投資する必要があるというものです。これは業界の周期的な性質によるもので、半導体企業はこの法則に従うのが困難です。図に示すように、ほとんどのシリコンウェーハメーカーはこの変化の影響を認識しており、過去数四半期で四半期ごとの総設備投資額をほぼ3倍に増やしました。厳しい市場環境にもかかわらず、これは依然として当てはまります。さらに興味深いのは、この傾向が長期間続いていることです。シリコンウェーハ企業は幸運であるか、他社が知らないことを知っています。半導体サプライチェーンは、未来を予測できるタイムマシンです。あなたの未来は、誰かの過去かもしれません。私たちは常に答えを得られるとは限りませんが、ほとんどの場合、価値のある質問を受けます。

投稿日時: 2024年6月17日